- 您现在的位置:买卖IC网 > Sheet目录3879 > PIC18F4539-E/ML (Microchip Technology)IC PIC MCU FLASH 12KX16 44QFN

PIC18FXX39

DS30485A-page 142

Preliminary

2002 Microchip Technology Inc.

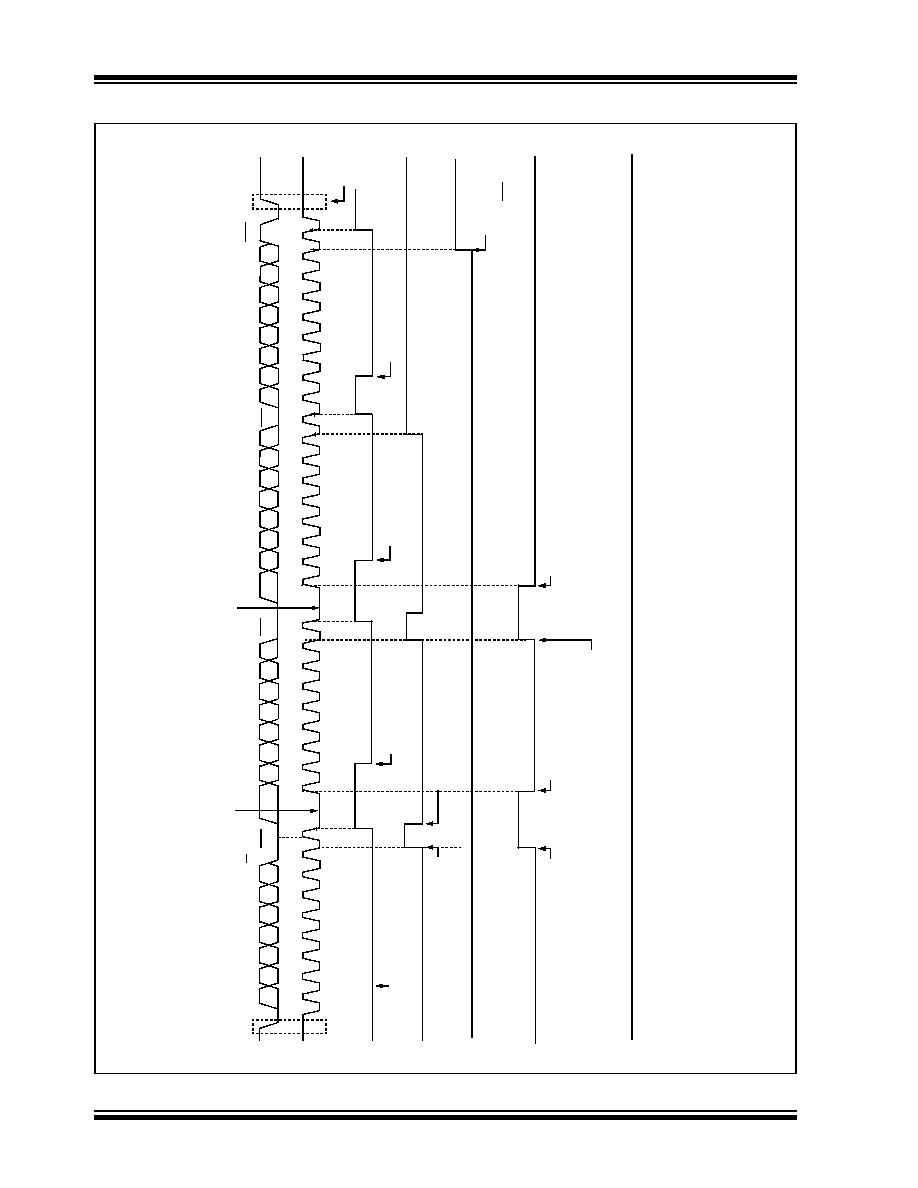

FIGURE 16-10:

I2C SLAVE MODE TIMING WITH SEN = 0 (RECEPTION, 10-BIT ADDRESS)

SDA

SCL

SS

PI

F

BF

(

S

SPS

TA

T

<

0

>

)

S

12

3

4

5

6

7

8

9

1

2

3

4

5

6

7

8

9

12

3

4

5

7

8

9

P

1

0

A

9

A

8

A

7

A

6

A

5

A

4A

3A

2

A

1

A

0

D

7

D

6

D

5

D

4

D

3

D

1

D

0

Re

ce

iv

eDa

ta

Byte

ACK

R/W

=

0

ACK

Re

ceive

F

irs

tB

yte

of

A

d

dr

ess

C

lea

re

di

n

s

o

ft

w

a

re

D2

6

(P

IR

1<

3>

)

C

lear

ed

in

so

ftw

are

R

e

ce

iv

eS

econd

B

yte

of

A

ddre

ss

C

le

a

red

by

har

dw

are

w

hen

S

P

A

D

is

update

d

w

ith

lo

w

byte

of

add

ress

UA

(

S

PST

A

T

<1

>)

Cl

ock

is

h

e

ld

lo

w

u

n

til

updat

e

of

S

P

A

D

has

ta

ken

pl

ac

e

UA

is

set

indicat

in

g

tha

t

the

S

P

A

D

need

sto

be

upda

ted

UA

is

set

in

dicating

that

S

P

A

D

need

sto

be

up

d

a

ted

C

le

ar

ed

by

har

dw

are

w

hen

SSP

ADD

is

u

p

d

ate

d

with

h

ig

h

by

te

of

addr

ess

S

SPB

UF

is

wr

itte

nwi

th

conten

ts

o

fS

S

P

S

R

D

um

m

y

re

a

do

fSS

PBUF

to

clear

B

F

flag

AC

K

CKP

12

3

4

5

7

8

9

D7

D6

D5

D4

D3

D1

D0

Re

ce

ive

Da

ta

B

yte

B

us

M

a

ste

r

term

inates

tran

sfer

D2

6

ACK

Cle

a

re

d

in

so

ftwa

re

Cle

a

re

d

in

so

ftw

ar

e

SSP

O

V

(

S

SPCO

N

<

6>

)

S

SPO

V

is

s

et

b

e

ca

u

se

S

SPB

UF

is

stil

lf

u

ll.

AC

K

is

no

tsent.

(C

K

P

do

es

not

reset

to

‘0

’w

hen

S

E

N

=

0)

Clo

ck

is

h

e

ld

lo

w

u

n

til

upda

te

of

S

P

A

D

has

ta

ken

p

la

ce

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC18F2539-E/SP

IC PIC MCU FLASH 12KX16 28DIP

PIC18F2539-E/SO

IC PIC MCU FLASH 12KX16 28SOIC

PIC18F4439-E/PT

IC PIC MCU FLASH 6KX16 44TQFP

PIC18F2439-E/SP

IC PIC MCU FLASH 6KX16 28DIP

PIC24F08KL401-I/SS

IC MCU 16BIT 8KB FLASH 20-SSOP

PIC16F689-I/SO

IC PIC MCU FLASH 4KX14 20SOIC

PIC16F689-I/ML

IC PIC MCU FLASH 4KX14 20QFN

PIC16F685-I/SO

IC PIC MCU FLASH 4KX14 20SOIC

相关代理商/技术参数

PIC18F4539-E/P

功能描述:8位微控制器 -MCU 24KB 1408 RAM 32 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4539-E/PT

功能描述:8位微控制器 -MCU 24KB 1408 RAM 32 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4539-I/ML

功能描述:8位微控制器 -MCU 24KB 1408 RAM 32 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4539-I/P

功能描述:8位微控制器 -MCU 24KB 1408 RAM 32 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4539-I/P

制造商:Microchip Technology Inc 功能描述:IC 8BIT FLASH MCU 18F4539 DIP40

PIC18F4539-I/PT

功能描述:8位微控制器 -MCU 24KB 1408 RAM 32 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4539IPT

制造商:MICRO CHIP 功能描述:NEW

PIC18F4539T-E/ML

功能描述:8位微控制器 -MCU 24KB 1408 RAM 32 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT